Beat Intel, Get Your 14 nm Process Development Kit Now!

on

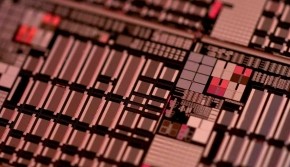

The industry’s first process development kit (PDK) for 14nm logic chips has been announced by Imec. This early-version PDK contains all elements for design assessment of the 14nm node through device compact models, parasitic extraction, design rules, parameterized cells (pcells), and basic logic cells. It anticipates the introduction of a number of new technologies like the use of FinFET transistors, which have a larger drive per unit footprint and higher performance at low supply voltages compared to the traditional planar technologies. Evolutions of this PDK will gradually also introduce the use of high-mobility channel materials. The PDK includes elements of both immersion- and EUV lithography, opening the way for a gradual transition from 193nm immersion to EUV lithography.

Starting from the PDK a first test chip is now being designed. This chip, planned for the second half of 2012, will allow testing the device-, interconnect-, process- and litho assumptions, as well as performance and power of circuits implemented at the tight area budgets of the 14nm node.

Discussion (0 comments)