CPU Family for Green Data Centres

on

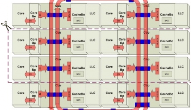

Intel’s new Xeon E5-2600 features a high-speed bi-directional ring bus surrounding up to eight cores, connecting up to 20 MB of cache, quad DDR3 memory controllers and 40 lanes of PCI Express 3.0 I/O. The new chip designed from the ground up and destined at data centers achieves a 70% increase in performance for the same energy consumption compared to its predecessors, according to the manufacturer.

This performance increase is achieved thanks to an on-chip power management agent that sets separate power limits for the whole device, the cores, memory and I/O, and then intelligently manages them for optimal performance, energy efficiency or other goals. Depending on load conditions and turbo requests, the E5 dynamically switches between performance mode, low-power mode and a new mode called balance mode, which accommodates turbo requests by adjusting the voltage and clock rate of other cores.

Along with voltage and frequency scaling for each core, the power management agent manages I/O energy efficiency by dynamically reducing I/O width in response to workload and thermal management goals. Core power can be scaled from 50 to 95 W, which also scales memory latency from 118 to 64 ns, while a unicore technique scales cache and ring clock rates to match.

Discussion (0 comments)