Python-based tool allows diagnosing dead-core boards

on

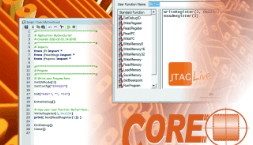

The JTAG Live CoreCommander tool from JTAG Technologies enables designers and engineers to activate the on-chip debug modes of a variety of popular processor cores to perform core-centric testing. The new tool includes support for ARM, XScale, PowerPC and TriCore architectures. The Python-based tool is suitable for diagnosing faults on dead-core boards during design, debug or repair, since no on-board code is required to perform memory reads and writes. It also increases fault coverage for production testing of boards populated with components having limited or non-existent boundary scan capability.

The tool can be used in either interactive mode or Python embedded mode. In interactive mode, the user first selects a supported device and then selects register access commands or memory read/write commands from an interactive window. Command sequences can be exported from the interactive window and replayed as Python scripts. The Python embedded mode allows functions to be embedded in Python code to create reusable test modules for specific tests.

Related information

Discussion (0 comments)