Review: TinyFPGA BX for open source FPGA development

Bitstreams

As with all FPGAs, to load a new configuration into the device, it must be fed a so-called “bitstream”. Large FPGA devices without NVCM require the bitstream to be loaded from external memory at every power-up, making it vulnerable to hacking and pirating attacks. For this reason the bitstream formats are kept secret, while modern large FPGAs even support encrypted bitstreams. The Lattice iCE40 bitstream however has been almost completely reverse-engineered (or “documented” as they call it) by the open-source community, allowing it to be used with open-source FPGA development tools.Open source tools for TinyFPGA

Apio is the tool of choice here. Inspired by PlatformIO, it is an open source multi-platform ecosystem for open FPGA boards like the TinyFPGA BX. Apio is a command-line interface (CLI) tool that uses Icestorm for synthesis, place & route and configuration to convert Verilog code to iCE40-compatible bitstreams.Amongst other useful tools, Apio supports Icarus Verilog for Verilog simulation and synthesis and — currently only on Windows — GTKWave as simulation viewer.Graphical tools

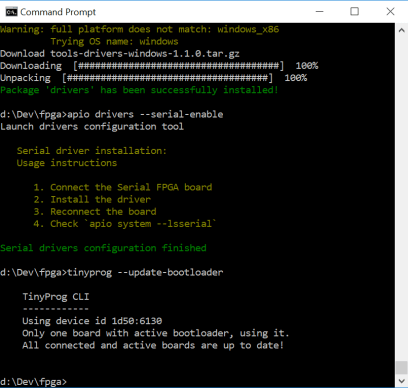

Because people have gotten used to and learned to appreciate graphical interfaces, Apio-IDE provides one based on Atom. Another one, Icestudio, an experimental visual hardware editor, features schematic entry.Installing everything is quite fast and easy as long as you have Python 3 installed on your computer. Then it is just a matter of entering a few installation commands. The ones given on the TinyFPGA BX User Guide work fine, except that I had to do an additional step:

When done connect the board to your computer and run the quick test:

Now that everything is working you can begin your journey through the fields of programmable logic.

Discussion (0 comments)