Surrounding-gate topology pushes Moore's law

on

The production of smaller and smaller semiconductor structures is an ongoing goal of much of semiconductor research. As structures approach single-atom dimensions the physical limit to Moores’s Law will be reached. Using a vertical ‘Surrounding-gate’ cell topology developed by Unisantis however allows a six-transistor SRAM cell to be squeezed into an incredibly small footprint of just 0.0184 to 0.0205 μm2. A cell using this SGT topology shows a 20 to 30% reduction in area compared to SGTs using a horizontal Gate-all-around FET structure. The vertical structure also brings other advantages including improved operating voltage, stability and leakage current.

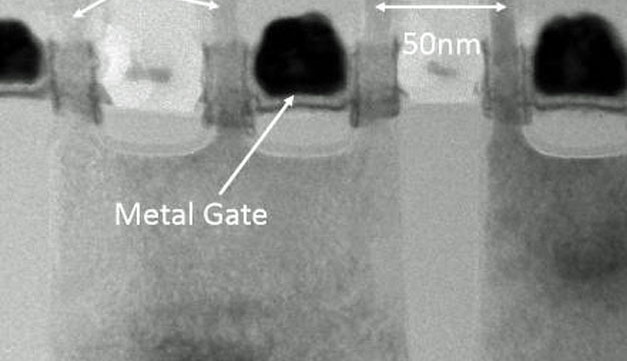

The use of vertical ‘surrounding-gate’ topology allows a near-perfect electrostatic control of the FET channel. An SRAM cell using this technique with a footprint of 0.0205 μm2 can be built with a minimum pillar pitch of 50 nm, resulting in a 24% better scaling factor compared to the smallest conventional SRAM cells. The manufacturing costs should be comparable to conventional finFET-based SRAMs providing the number of processes can be optimized by using single-exposure EUV lithography techniques.

Discussion (0 comments)