Run Linux on a 64-bit Quad-core RISC-V Processor

December 19, 2017

on

on

SiFive has released an open-source RISC-V architecture, 64-bit, quad-core application processor aimed at full-featured operating systems such as Linux.

According to SiFive, “The release of the U54-MC Coreplex marks the architecture’s expansion into the application processor space — opening entirely new use cases for RISC-V. It is ideal for applications which need full operating system support such as AI, machine learning, networking, gateways and smart IoT devices.”

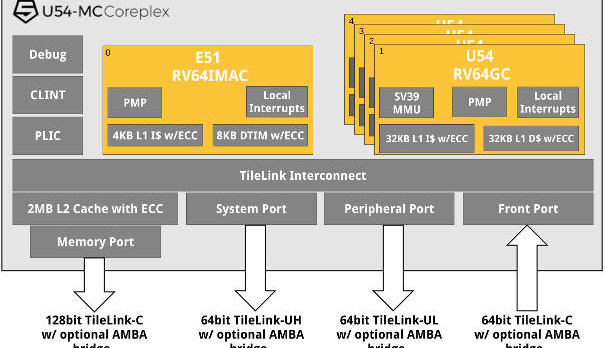

The standard U54-MC contains four U54 CPUs along with a single E51 CPU and supports cache coherence. Each U54 CPU has a five-stage in-order pipeline, and supports the RV64GC ISA. The 64-bit E51 CPU serves as a management core and is fully-coherent with the main U54 cores.

SiFive’s U54-MC Coreplex has been taped out as part of SiFive’s “Freedom Unleashed” family of customisable RISC-V SoCs. As implemented in the platform, the U54 and E51 CPUs run at >1.5 GHz in 28-nm silicon. Each of the U54 CPUs has a 32-Kbyte instruction cache and 32-Kbyte data cache, and all of the cores share a coherent, 2-Mbyte level-2 cache.

Customers can license the U54-MC Coreplex in a variety of configurations besides the 4+1 default configuration.

A development board will be available in the first quarter next year.

According to SiFive, “The release of the U54-MC Coreplex marks the architecture’s expansion into the application processor space — opening entirely new use cases for RISC-V. It is ideal for applications which need full operating system support such as AI, machine learning, networking, gateways and smart IoT devices.”

The standard U54-MC contains four U54 CPUs along with a single E51 CPU and supports cache coherence. Each U54 CPU has a five-stage in-order pipeline, and supports the RV64GC ISA. The 64-bit E51 CPU serves as a management core and is fully-coherent with the main U54 cores.

SiFive’s U54-MC Coreplex has been taped out as part of SiFive’s “Freedom Unleashed” family of customisable RISC-V SoCs. As implemented in the platform, the U54 and E51 CPUs run at >1.5 GHz in 28-nm silicon. Each of the U54 CPUs has a 32-Kbyte instruction cache and 32-Kbyte data cache, and all of the cores share a coherent, 2-Mbyte level-2 cache.

Customers can license the U54-MC Coreplex in a variety of configurations besides the 4+1 default configuration.

A development board will be available in the first quarter next year.

Read full article

Hide full article

Discussion (0 comments)