Are NC-FETs the way forward?

March 21, 2019

on

on

Over the last half century advances in miniaturization have ensured that Moore’s prediction of integrated circuit component density has remained more or less true. One sticking point of MOSFET miniturisation has been a fundamental property known as the Boltzmann distribution of electrons—also known as the Boltzmann Tyranny which sets the theoretical minimum thermionic limit to a MOSFET’s subthreshold slope (SS) characteristic at 60 mV/dec (at room temperature). This means you can’t keep reducing the operating voltage to get lower power consumption. Considering how many MOSFETs are packed into a chip, this fundamental limit is quite a big deal.

Since then, many research teams have invested time into developing this promising new FET model. Professor Peide Ye at Purdue university has acknowledged the wide scatter of research results and thinks its time we coordinated the efforts and applied an integrated and comprehensive analysis to the existing data set.

Professor Ye and colleagues have published a paper ‘A critical review of recent progress on negative capacitance field-effect transistors‘ in Applied Physics Letters available free. In there he poses three basic questions:

Given the unique physics of the gate stack, would the technology be reliable and immune from gate dielectric breakdown, negative bias temperature instability, hot carrier degradation, and other perspectives.

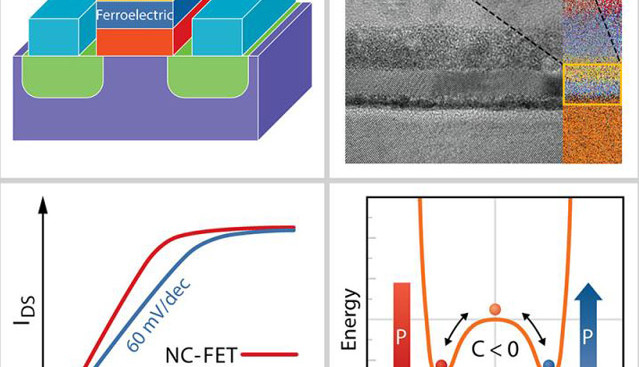

Ten years down the line

Back in 2008 it was suggested that the introduction of a thin-layer of ferroelectric (FE) material to the existing gate oxide of a MOSFET would make a dramatic change in the device characteristics and produce complete disappearance of ferroelectric hysteresis (ΔV). The internal voltage at the FE-oxide interface would be higher than the gate voltage, so that the SS characteristic will drop below the Boltzmann limit of 60 mV/dec. This novel structure called an NC-FET (Negative-Capacitance FET) would allow operation at a lower supply voltage giving reduced power consumption. The threshold voltage would actually increase as supply increases which also makes transistor scaling much simpler.Since then, many research teams have invested time into developing this promising new FET model. Professor Peide Ye at Purdue university has acknowledged the wide scatter of research results and thinks its time we coordinated the efforts and applied an integrated and comprehensive analysis to the existing data set.

Professor Ye and colleagues have published a paper ‘A critical review of recent progress on negative capacitance field-effect transistors‘ in Applied Physics Letters available free. In there he poses three basic questions:

- Can a capacitor be negative?

- Given the domain dynamics, can a ferro-electric-based capacitor or FET show negative capacitance?

Are the reported transient and steady-state experiments conclusive? - Even if a ferroelectic-dielectric can be stabilised in the negative capacitance state, are the dimensions suitable for transistors beyond the 5nm technology node?

Given the unique physics of the gate stack, would the technology be reliable and immune from gate dielectric breakdown, negative bias temperature instability, hot carrier degradation, and other perspectives.

Read full article

Hide full article

Discussion (0 comments)