New microchip improves efficient data centers

on

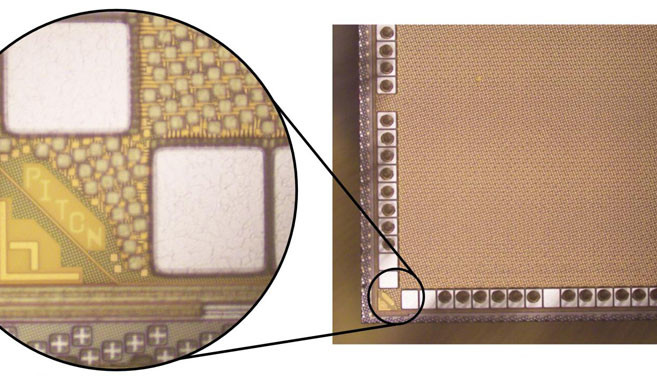

Researchers at Princeton University in New Jersey, USA have designed a microchip which should improve the performance of data centers for e-mail and social media services. The researchers have targeted the chip, called Piton, for application in large computer systems. The architecture of the chip is also scalable, so that it can be used for systems ranging from tens of cores to systems with thousands of cores.

The present version of the chip measures 6x6 mm and has more than 460 million transistors, each 32 nm 'large'. The majority of those are in 25(!) cores. These 'recognize' the operations asked for by users and carry these out in sequence, which should save about 20% of energy compared to a standard core. A second innovation is the implementation of a ‘memory traffic shaper’, which directs the data traffic between the cores and external memory in an optimal way. This is good for a gain of 18%, according to the researchers. And, last but not least, the cache memory has also been redesigned.

More information: www.openpiton.org.

Discussion (0 comments)